05 最快的存储器 - Cache

Cache 是什么

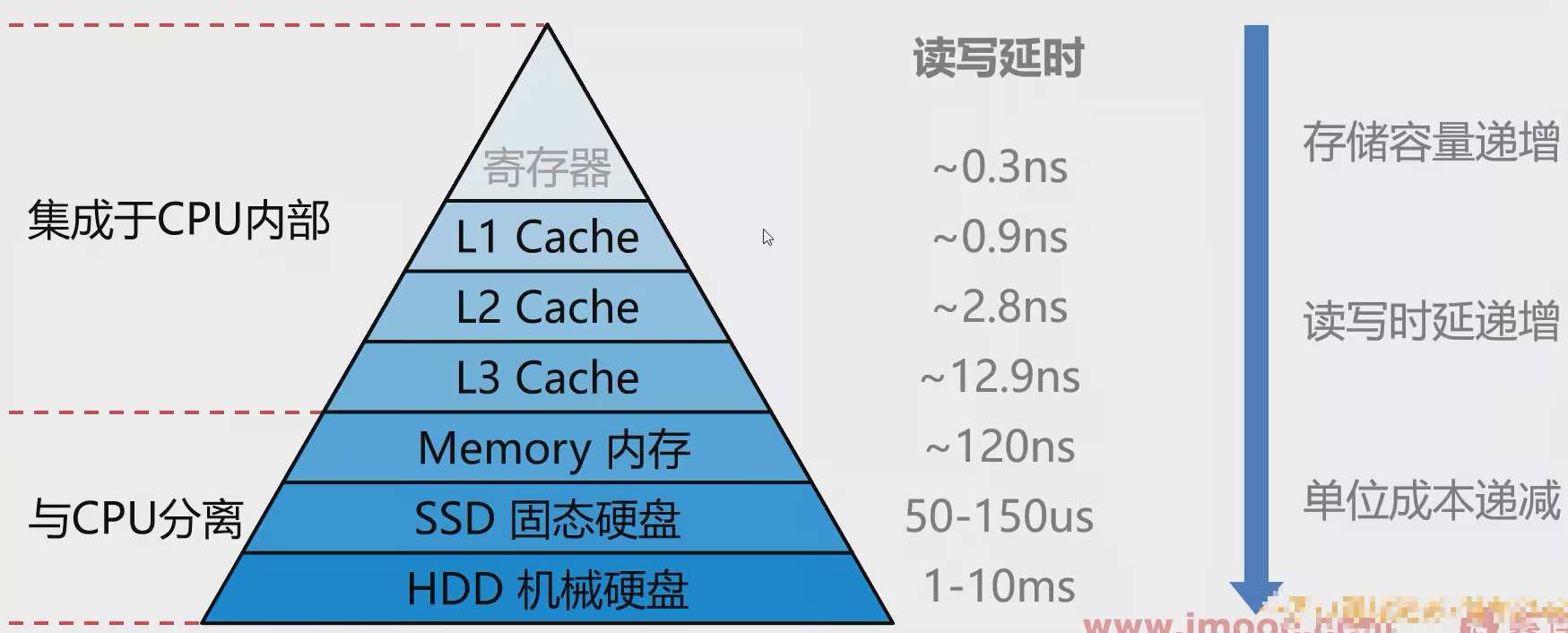

- Cache,中文译为高速缓冲存储器;

- 一种位于 CPU 内部的高速缓存;

- 用于存储 CPU 频繁访问的数据和指令;

- 缓存命中可以有效减少 CPU 访问内存的次数;

- 通常由多级缓存组成,每级缓存的容量和速度均不同;

- 一般分为 L1 Cache、L2 Cache、L3 Cache,容量和访问时延逐级增加;

Cache 与资源共享

- L1 Cache:分为 L1i Cache 和 L1d Cache,每个逻辑核独属;

- L2 Cache:每个物理核独属,两个逻辑核共享;

- L3 Cache:NUMA 上的所有物理核共享;

Linux 查看 Cache 容量

bash

➜ ~ lscpu | grep "cache:"

L1d cache: 128 KiB (4 instances)

L1i cache: 128 KiB (4 instances)

L2 cache: 16 MiB (4 instances)

L3 cache: 16 MiB (1 instance)

➜ ~ lscpu

Architecture: x86_64

CPU op-mode(s): 32-bit, 64-bit

Address sizes: 48 bits physical, 48 bits virtual

Byte Order: Little Endian

CPU(s): 4

On-line CPU(s) list: 0-3

Vendor ID: AuthenticAMD

BIOS Vendor ID: Smdbmds

Model name: AMD EPYC 7K62 48-Core Processor

BIOS Model name: 3.0

CPU family: 23

Model: 49

Thread(s) per core: 1

Core(s) per socket: 4

Socket(s): 1

Stepping: 0

BogoMIPS: 5190.24

Flags: fpu vme de pse tsc msr pae mce cx8 apic sep mtrr pge mca cmo

v pat pse36 clflush mmx fxsr sse sse2 ht syscall nx mmxext f

xsr_opt pdpe1gb rdtscp lm rep_good nopl cpuid extd_apicid ts

c_known_freq pni pclmulqdq ssse3 fma cx16 sse4_1 sse4_2 x2ap

ic movbe popcnt aes xsave avx f16c rdrand hypervisor lahf_lm

cmp_legacy cr8_legacy abm sse4a misalignsse 3dnowprefetch o

svw topoext ibpb vmmcall fsgsbase bmi1 avx2 smep bmi2 rdseed

adx smap clflushopt sha_ni xsaveopt xsavec xgetbv1 arat

Virtualization features:

Hypervisor vendor: KVM

Virtualization type: full

Caches (sum of all):

L1d: 128 KiB (4 instances)

L1i: 128 KiB (4 instances)

L2: 16 MiB (4 instances)

L3: 16 MiB (1 instance)

NUMA:

NUMA node(s): 1

NUMA node0 CPU(s): 0-3

Vulnerabilities:

Gather data sampling: Not affected

Itlb multihit: Not affected

L1tf: Not affected

Mds: Not affected

Meltdown: Not affected

Mmio stale data: Not affected

Reg file data sampling: Not affected

Retbleed: Mitigation; untrained return thunk; SMT disabled

Spec rstack overflow: Vulnerable: Safe RET, no microcode

Spec store bypass: Vulnerable

Spectre v1: Mitigation; usercopy/swapgs barriers and __user pointer sani

tization

Spectre v2: Mitigation; Retpolines; IBPB conditional; STIBP disabled; RS

B filling; PBRSB-eIBRS Not affected; BHI Not affected

Srbds: Not affected

Tsx async abort: Not affectedbash

➜ ~ cat /sys/devices/system/cpu/cpu0/cache/index0/size

32K

➜ ~ cat /sys/devices/system/cpu/cpu0/cache/index1/size

32K

➜ ~ cat /sys/devices/system/cpu/cpu0/cache/index2/size

4096K

➜ ~ cat /sys/devices/system/cpu/cpu0/cache/index3/size

16384K

➜ ~ cat /sys/devices/system/cpu/cpu0/cache/index*/size

32K

32K

4096K

16384K存储器的层次结构